I'm fairly experienced at gcc hacking but am having trouble wrapping my mind around this particular xtensa architecture.

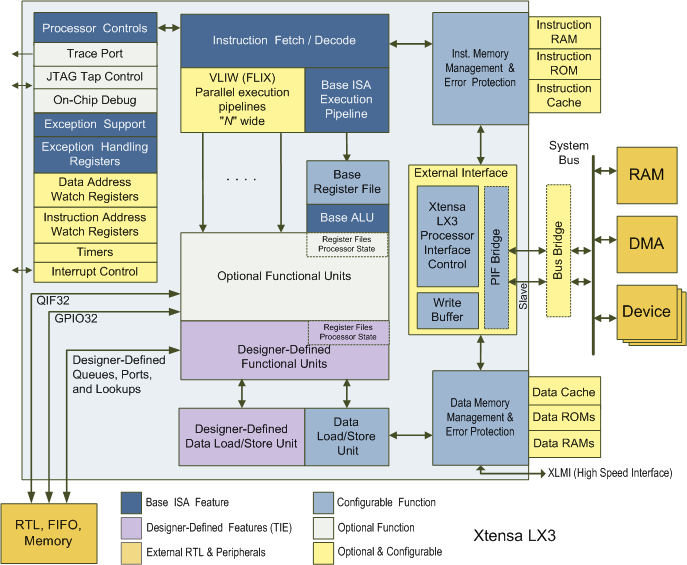

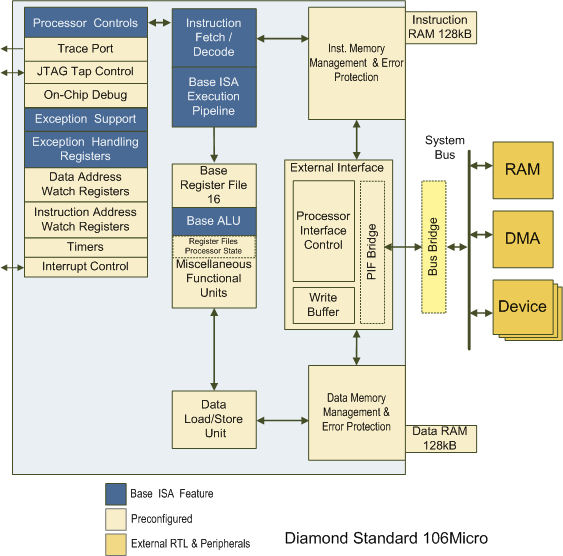

I noticed in another topic it was discovered that this chip is lx106 (did I get that right?) so it's not actually using any custom instructions -- it's an "off the shelf" xtensa architecture.

If you have access to or can write a little about the chip architecture and its instruction set, that would help! Especially if you can describe how the chip architecture differs from what gcc currently supports, though I would guess that's something not 100% known at this time.